# F3851/F3856 Program Storage Unit

# **Microprocessor Product**

# Description

The Fairchild F3851 and F3856 are the principal program storage devices for the F8 microcomputer system. The F3851 provides 1024 bytes of ROM; the F3856 provides 2048 bytes. The program storage unit (PSU) is customized with programs and permanent data tables, which are specified as ROM masks.

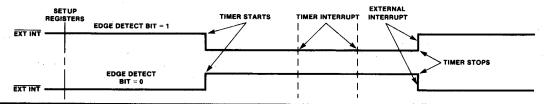

The PSU devices have two 8-bit, bidirectional I/O ports, interrupt logic, a programmable timer, and a pulse width measurement circuit. They also contain memory addressing logic with data counters and program counters. The interrupt logic responds to requests from an external device and internally from the timer. The pulse width measurement circuit (F3856) is a combination of these two capabilities.

The PSU devices are manufactured using N-channel, isoplanar MOS technology; therefore, power dissipation is very low, typically less than 275 mW.

- 1024/2048 Bytes of Program Storage

- Internal Memory Addressing Logic

- 16 Bidirectional, Individually Controlled I/O Lines, Organized as Two 8-Bit Ports

- Programmable Timer (F3856) Preset, Start, Stop, and Read-Back Ability; Four Selectable Timer Count Rates, and Pulse Width Measurement

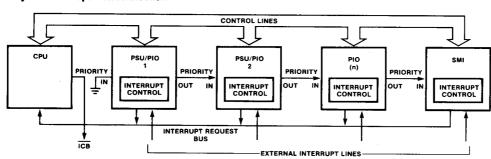

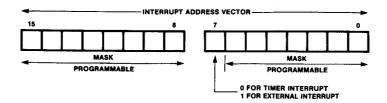

- Full Interrupt Level Dalsy-Chain Expandable, Independent Interrupt Address Vectors for Timer and External Interrupt

- 2 MHz Operation

- TTL and LSTTL Compatible

- Low Power Dissipation, Typically Less Than 275 mW

- +5 V and +12 V Power Supplies

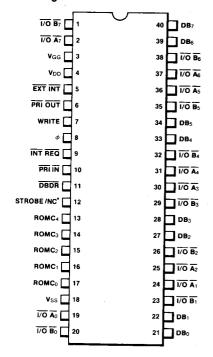

#### **Connection Diagram**

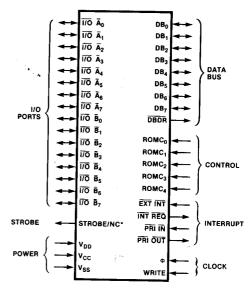

# **Signal Functions**

\*NC for F3851 only.

# **Device Organization**

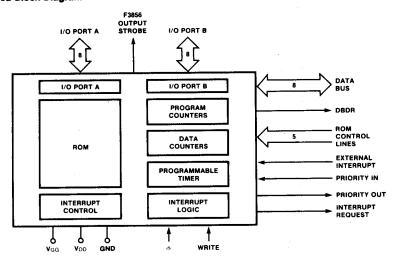

The PSU is more than a read-only memory unit: every memory device within the F8 system contains its own memory addressing logic along with associated address registers. Refer to figure 1 for a simplified block diagram of the PSU. A single 8-bit data bus provides all necessary communication between a PSU (or any other memory device) and an F3850 CPU.

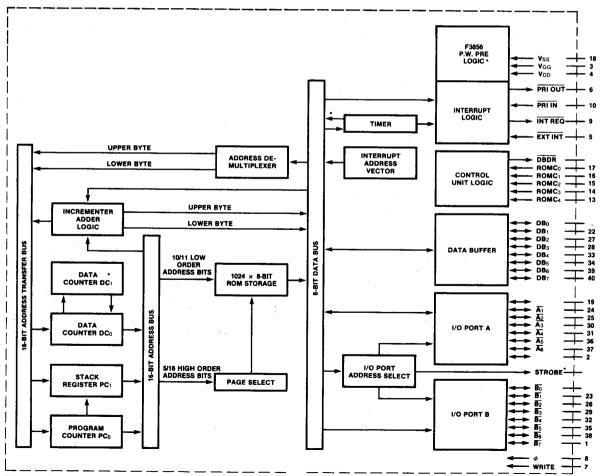

The PSU has an elementary arithmetic unit that can increment and add 16-bit data units; for memory addressing logic, these two operations are sufficient. The PSU is functionally illustrated in figure 2. These devices also contain a control unit that decodes the five read-only memory control (ROMC) lines, generated by the CPU, as though they were a 5-bit instruction code. Similar to the CPU, the PSU generates internal signals to control data flow and arithmetic logic within itself. One control output, data bus drive (DBDR), is generated to coincide with data being output by the PSU.

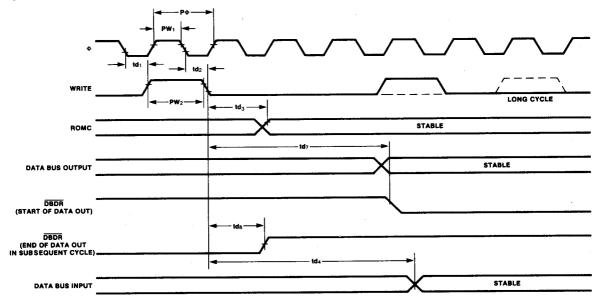

#### System Clock Timing

All timing within the F3851/F3856 PSU is controlled by the \$\( \phi\) and WRITE signals, which are generated from the F3850 CPU. Refer to the F3850 data sheet for a description of these clock signals, The WRITE clock refreshes and updates PSU address registers, which are dynamic. The \$\( \phi\) clock drives sequencing logic to precharge the ROM matrix; it also drives the programmable timer.

#### I/O Ports

The unit contains four preassigned I/O port addresses: the two lowest are assigned to I/O ports A and B and are used to transfer data to and from external devices. The other two I/O addresses are assigned to the programmable timer and the interrupt control register and are treated as I/O ports. Associated with the I/O ports is an I/O port address select register (ASR). This is a 6-bit register for the F3851 and a 5-bit register for the F3856. The contents are a mask option, which must be specified at the time the PSU is created. The ports are addressed as follows:

XXXXXX00 I/O port A XXXXXXX01 I/O port B

XXXXXX10 Interrupt control register

XXXXXX11 Programmable timer

Figure 1 PSU Simplified Block Diagram

For example, if the six binary digits are 000010, the four I/O port addresses are H'08', H'09', H'0A', and H'0B'.

When a logic 1 is output to I/O port A or B, it places a 0 V level on the output pin. This same inverted logic applies to input.

The F3851 I/O ports, timer, and interrupt control register are not initialized during the power-on reset cycle. The F3856 I/O ports and interrupt control register are initialized during both the power-on or external reset cycle; the timer register is not initialized during power-on or external reset cycles.

# ROM Addressing

The F3851 8K PSU has 1024 bytes of read-only memory; the F3856 16K PSU has 2048 bytes. This ROM array may contain object program code and/or tables of nonvarying data. Every PSU is implemented using a custom mask that specifies the state of every ROM bit and certain address mask options that are external to the ROM array.

Figure 2 PSU Functional Diagram

The ROM addressing logic consists of 16-bit registers: program counter PC<sub>0</sub>, stack register PC<sub>1</sub>, and data counter DC<sub>0</sub>. Data counter DC<sub>1</sub> is provided on the F3856 as an additional buffer for DC<sub>0</sub>.

A 6-bit page select register and 10-bit address select register provide decode logic for the F3851. The F3856 uses a 5-bit page select register and an 11-bit address select register.

Program Counter, Data Counter, and Stack Registers

Program counter PC $_0$  always addresses the memory location out of which the next program instruction byte is read. If the instruction requires data (i.e., an operand) to be accessed, data counter DC $_0$  must address memory for this purpose; PC $_0$  cannot be used to address data, since it is saving the address of the next instruction code. By using the exchange DC instruction in the F3856 program, the two data counter contents of DC $_0$  and DC $_1$  can be exchanged.

The provision of two address registers, PC<sub>0</sub> and DC<sub>0</sub>, is a convenience to the F3850 CPU and is not a necessary part of the memory addressing logic sequence within a PSU. Address decoding is identical, whether originating in PC<sub>0</sub> or DC<sub>0</sub>.

The  $PC_0$ ,  $PC_1$ , and  $DC_0$  are loaded from two consecutive single-byte inputs on the data bus;  $PC_1$  and  $DC_0$  are transmitted as two single-byte outputs on the data bus. The contents of  $DC_0$  and  $DC_1$  of F3856 can be exchanged in one instruction.

Stack register PC<sub>1</sub> is a buffer for program counter PC<sub>0</sub>; the contents of PC<sub>1</sub> are never used directly to address memory. When an interrupt is acknowledged, the contents of PC<sub>0</sub> are saved in PC<sub>1</sub>.

# Page Select and Address Select Registers

All memory addresses are 16 bits wide, whether originating in the program counter or in the data counter. Address decode logic within the PSU separates the 16-bit address into two portions: the low order addresses the ROM storage bytes; the high order addresses the page.

|       | High-Order<br>Byte Address | Low-Order<br>Page Address  |

|-------|----------------------------|----------------------------|

| F3851 | 1024 Byte Select<br>6 Bits | 64 Page Options<br>10 Bits |

| F3856 | 2048 Byte Select<br>5 Bits | 32 Page Options<br>11 Bits |

If the high-order bits of the address coincide exactly with the page select mask, an enable signal is generated, causing the PSU logic to respond to a memory access request. If the high-order bits of the address do not coincide exactly with the page select, no enabling signal is generated and the PSU does not respond to memory access requests.

The page select register identifies the memory addressing space of the individual PSU device. Each of the 32 (or 64) page select options allowed by the 5-bit (or 6-bit) page select register identifies a single address space consisting of 2048 (or 1024) continguous memory addresses.

# Incrementer Adder Logic

There are only two arithmetic operations that memory devices need to perform on the contents of memory address registers:

- Increment by 1 the 16-bit value stored in address PC<sub>0</sub> or DC<sub>0</sub>.

- 2. Add an 8-bit value, treated as a signed binary number (subject to twos complement arithmetic) to the 16-bit value stored in an address register. If the 8-bit value is being treated as a signed binary number, the high-order bit of the 8-bit value is the sign bit; the sign bit must be propagated through the missing high-order eight bits.

The PSU control unit implements the incrementer adder logic through control signals internal to PSU device logic.

# Addressing Consistency in Multiple Memory Devices

When an ROMC state specifies a memory access, only one memory device responds to the memory access operation itself. However, every memory device responds to ROMC states that call for modifying the contents of a program counter or data counter register. Providing every memory device that is connected to the 8-bit data bus of an F3850 CPU is also connected to the ROMC control lines of the same CPU, address contentions cannot arise. Every memory device simultaneously receives the same ROMC state signals from the CPU; every memory device responds to ROMC states by identically modifying the contents of memory address registers, if such modifications are specified. Therefore, every PC<sub>0</sub> register on every memory device always contains identical information; the same is true for DC<sub>0</sub> and PC<sub>1</sub> registers.

Only one memory device (the one whose address space includes the specified memory address) actually responds to any memory access request. To avoid addressing conflicts, it is only necessary to ensure that the following conditions exist:

**Signal Descriptions**The PSU input and output signals are described in table 1.

Table 1 PSU Signal Descriptions

| Mnemonic                                            | Pin No.               | Name                        | Description                                                                                       |

|-----------------------------------------------------|-----------------------|-----------------------------|---------------------------------------------------------------------------------------------------|

| Clock                                               |                       |                             |                                                                                                   |

| ♦<br>M/DITE                                         | 8                     | Clock                       | The two clock input signals that originate at the                                                 |

| WRITE                                               | 7                     |                             | F3850 CPU.                                                                                        |

| I/O Ports<br>I/O A <sub>0</sub> -I/O A <sub>7</sub> | 19, 24, 25,           | I/O Ports A                 | Pidirectional parts through which the DIO                                                         |

|                                                     | 30, 31, 36,           | "O TOILS A                  | Bidirectional ports through which the PIO communicates with logic external to the                 |

|                                                     | 37, 2                 |                             | microprocessor system.                                                                            |

| I/O B <sub>0</sub> -I/O B <sub>7</sub>              | 20, 23, 26,           | I/O Ports B                 |                                                                                                   |

|                                                     | 29, 31, 35,           |                             |                                                                                                   |

|                                                     | 38, 1                 |                             |                                                                                                   |

| Control                                             | 47.40.45              | Decide 1                    |                                                                                                   |

| ROMC <sub>0</sub> −ROMC <sub>4</sub>                | 17, 16, 15,<br>14, 13 | Read-Only<br>Memory Control | Input signals that originate at the F3850 CPU control internal functions of the PSU.              |

| <br>Data Bus                                        | 14, 10                | Michiery Control            | control internal functions of the FSO,                                                            |

| DB <sub>0</sub> -DB <sub>7</sub>                    | 21, 22, 27,           | Data Bus                    | Bidirectional 3-state lines that link the PSU to all                                              |

| • •                                                 | 28, 33, 34,           |                             | other devices within the microprocessor system.                                                   |

|                                                     | 39, 40                |                             |                                                                                                   |

| DBDR                                                | 11                    | Data Bus Drive              | A low output, open-drain signal that indicates the                                                |

|                                                     |                       |                             | data bus currently contains data flowing from the PSU.                                            |

| Strobe                                              |                       |                             | PSU.                                                                                              |

| STROBE                                              | 12                    | Strobe                      | This output signal provides a positive pulse                                                      |

|                                                     |                       | 0000                        | whenI/O port A is being read by an input instruc-                                                 |

|                                                     |                       |                             | tion or is being updated by an output instruction                                                 |

|                                                     |                       |                             | (F3856).                                                                                          |

| Interrupt<br>EXT INT                                | 5                     | External Interrunt          | A high to low translation on this issued stood to                                                 |

| EXT IIV                                             | 3                     | External Interrupt          | A high-to-low transition on this input signal is interpreted as an interrupt request from an      |

|                                                     |                       |                             | external device.                                                                                  |

| INT REQ                                             | 9                     | Interrupt Request           | This output signal is the INT REQ input to the                                                    |

|                                                     |                       |                             | F3850 CPU; it must be output low to interrupt the CPU, which occurs only if PRI IN is low and PSU |

|                                                     | '                     | *                           | interrupt control logic is requesting an interrupt.                                               |

| PRI IN                                              | 10                    | Priority In                 | Unless this input signal is low, the PSU does not                                                 |

|                                                     |                       |                             | set the INT REQ signal low in response to an                                                      |

| PRI OUT                                             | 6                     | Briania. Out                | interrupt.                                                                                        |

| 1111 001                                            | "                     | Priority Out                | This output signal becomes the PRI IN signal to the next device in the interrupt-priority daisy   |

|                                                     |                       |                             | chain; it is output high unless the PRI IN signal is                                              |

|                                                     |                       |                             | entering the PSU low and the PSU is not                                                           |

| Power                                               | <del> </del>          |                             | requesting an interrupt                                                                           |

| V <sub>DD</sub>                                     | 4                     | Power Supply                | +5 V ±5%                                                                                          |

| $V_{GG}$                                            | 3                     | Power Supply                | +12 V ±5%                                                                                         |

| V <sub>SS</sub>                                     | 18                    | Ground                      | System ground — 0 V; V <sub>DD</sub> and V <sub>GG</sub> are referenced                           |

|                                                     | '-                    |                             | to V <sub>SS</sub> .                                                                              |

- All memory devices must receive the same ROMC state signals from one CPU and must contain identical information.

- Page select masks must not be duplicated more than one memory device cannot have the same memory space.

- The memory address contained in the specified register (PC<sub>0</sub> or DC<sub>0</sub>) must be within the memory space of at least one memory device.

### **ROMC States**

Table 2 lists the data bus contents as a function of ROMC states.

#### Instruction Execution

The PSU responds to signals that are output by the F3850 CPU in the course of implementing instruction cycles. Refer to table 2 for a summary of the data bus response to the ROMC states generated by the CPU.

# **Data Output by the PSU**

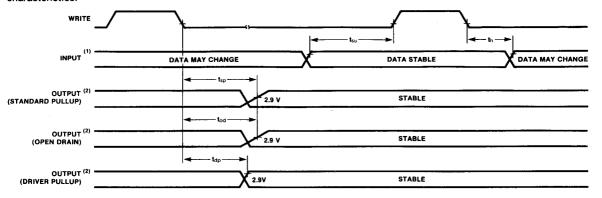

Figure 3 provides timing when the PSU outputs data on the

Figure 3 Data Bus Timing

data bus. This timing applies whenever a PSU is the data source. The PSU places data on the data bus, even in the

worst case, in time for the setup required by any F3850 CPU destination (refer to the F3850 CPU data sheet).

Table 2 Data Bus Contents as a Function of the ROMC State

| ROMC State | If F3851/F3856 PSU is the Source*                               | If F3850 CPU is the Source |                                  |

|------------|-----------------------------------------------------------------|----------------------------|----------------------------------|

| (Hex)      | Description of Data                                             | Address**                  | Description of Data              |

| 00         | Instruction                                                     | PC <sub>0</sub>            |                                  |

| 01         | Offset for branch                                               | PC <sub>0</sub>            |                                  |

| 02         | Operand                                                         | DC <sub>0</sub>            |                                  |

| 03         | Operand                                                         | PC <sub>0</sub>            |                                  |

| 04         |                                                                 | ' '                        |                                  |

| 05         |                                                                 |                            | Byte to be stored                |

| 06         | Upper byte, DC <sub>0</sub>                                     |                            | Dyto to be stored                |

| 07         | Upper byte, PC <sub>1</sub>                                     | }                          |                                  |

| 08         | 1 (1)                                                           |                            | = 00 for PC <sub>n</sub>         |

| 09         | Lower byte, DC <sub>0</sub>                                     |                            | = 00 101 FO0                     |

| 0A         |                                                                 |                            | Offset for DC <sub>0</sub>       |

| 0B         | Lower byte, PC <sub>1</sub>                                     |                            | Offset for DC0                   |

| 0C         | Byte for PC <sub>0</sub> , lower                                | PC <sub>0</sub>            |                                  |

| 0D         |                                                                 | [00]                       |                                  |

| 0E         | Byte for DC <sub>0</sub> , lower                                | PC <sub>0</sub>            |                                  |

| OF         | Lower byte of interrupt vector if it is source of the interrupt |                            |                                  |

| 10         |                                                                 | 1                          |                                  |

| 11         | Byte for DC <sub>0</sub> , upper                                | PC <sub>0</sub>            |                                  |

| 12         |                                                                 | "~                         | Byte for PC <sub>0</sub> , lower |

| 13         | Upper byte of interrupt vector if it is source of the interrupt |                            | Byte for PC <sub>0</sub> , lower |

| 14         |                                                                 |                            | Byte for PC <sub>0</sub> , upper |

| 15         | •                                                               | 1.                         | Byte for PC <sub>1</sub> , upper |

| 16         |                                                                 |                            | Byte for DC <sub>0</sub> , upper |

| 17         |                                                                 | 1                          | Byte for BC lower                |

| 18         |                                                                 |                            | Byte for PC <sub>0</sub> , lower |

| 19         |                                                                 | 1.                         | Byte for PC <sub>1</sub> , lower |

| 1A         |                                                                 |                            | Byte for DC <sub>0</sub> , lower |

| 1B         | Byte from I/O register, if selected                             |                            | Byte for selected I/O port       |

| 1C         | - 7.5                                                           | ļ .                        | (Nictor 1)                       |

| 1D         |                                                                 | ]                          | (Note 1)                         |

| 1E         | Lower byte, PCo                                                 | 1                          |                                  |

| 1F         | Upper byte, PC <sub>0</sub>                                     | 1                          |                                  |

<sup>\*</sup>Only drives the data bus within the segment of address space that belongs to the PSU.

#### Note 1

During INS or OUTS instruction for port 0 or 1: I/O byte During INS or OUTS instruction for port 4-F: I/O address During all other instructions, F3850 does not drive.

<sup>\*\*</sup>An entry in this column specifies the register from which a memory address was obtained.

The data bus drive signal (DBDR) is low, while data output by the PSU is stable on the data bus. Thus, a DBDR low signal indicates that the data bus currently contains data flowing from a PSU. For systems with more than one PSU, the DBDR outputs can be wire-ORed and the result used as a bus data flow direction indicator. The DBDR signal remains low until timing delay tdg into the instruction cycle following the one in which DBDR was set low.

#### Data Input to the PSU

When the PSU receives data off the data bus, in the worst case, the data must be added to a 16-bit number within the PSU adder/incrementer. This worst case corresponds to data coming from the accumulator of the CPU for an ADC instruction or from a memory device for a BR instruction. For this worst case, arriving data must allow sufficient time for 16-bit adder logic (time delay  $td_4$  in figure 3 identifies this worst-case timing).

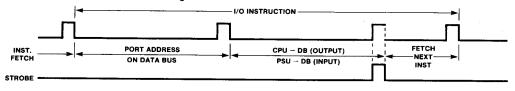

#### **PSU Input/Output Interfacing**

The I/O ports with addresses XXXXXX00 and XXXXXX01 (XXXXXX is the 6-bit I/O port address select) are used to transmit data between the PSU and external devices. The IN and INS instructions cause data at the I/O ports to be transmitted to the CPU; the OUT and OUTS instructions cause data in the CPU accumulator to be loaded into an I/O port. Each I/O pin has an output latch that holds the pin DC data.

Input and output operations using the two PSU I/O ports execute in three instruction cycles. During the first cycle, the port address is transmitted to the data bus. During the second cycle, data is either sent from the accumulator to the I/O latch or enabled from the I/O pin to the accumulator, depending on whether the instruction is an output or an input. At the falling edge of the WRITE signal (marking the end of the second cycle and beginning of the third cycle), the data is strobed into either the latch (OUTS) or the accumulator (INS), respectively. The third cycle is then used by the CPU for its next instruction fetch.

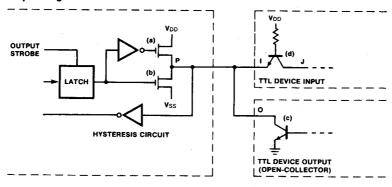

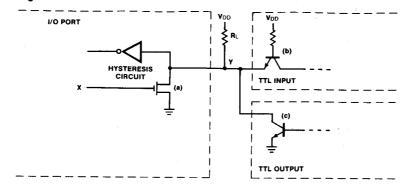

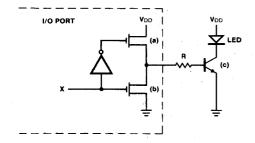

#### I/O Port Options

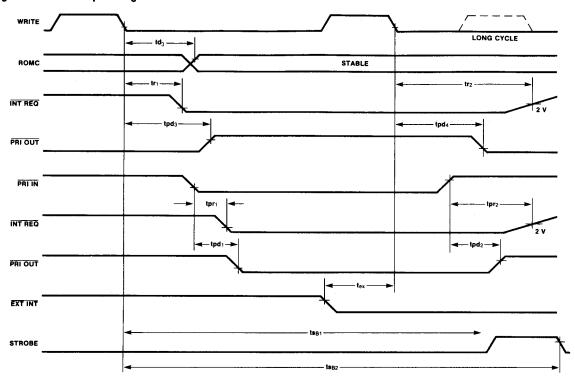

Data bus timing associated with the execution of I/O instructions does not differ from data bus timing associated with any other data transfer to or from the PSU. However, timing at the I/O port itself depends on which port option is being used. Figures 4, 5, and 6 illustrate the three port options; figure 7 illustrates timing for the three cases.

Standard Pull-Up Configuration (Figure 4)—All I/O port bits should be set for a high level, before data input, to prevent incoming logic 0s from being masked by logic 1s preset at the port from previous outputs. In some instances, the ability to mask bits of a port to logic 1 is useful. (Note that logic 1 becomes a 0 V electrical level at the I/O pin; logic 0 corresponds to a high electrical level.)

Each I/O port pin is a wire-AND structure between an internal latch and an external signal, if any. The latch is always loaded directly from the accumulator. Each I/O pin is set high or low under program control. If a 1 (high) is presented at the latch, gate (b) turns on and gate (a) turns off, so that P is at  $V_{SS}$  (low). If a 0 (low) is presented at the latch, gate (a) turns on and gate (b) turns off, so that P is at  $V_{DD}$  (high).

When data is output through an I/O port, the pin is connected directly to a standard TTL gate input. Data is input to the pin from a TTL output. In normal operation, high or low levels at P drive the external TTL device input transistor (d). If a low level is set at P, transistor (d) conducts current through the path J, I, P, and FET (b). This is transferred as a low level to the rest of the circuits in the TTL device and results in a high or low level at the output of the device, depending on its characteristics. If the level at P is set high, transistor (d) cuts off and a high level is transferred by (d). When data is input to the I/O pin, a high or low signal at the pin transfers a logic 1 or 0 to the accumulator.

Since the I/O pin and the TTL device output at 0 are wire-ANDed, it is possible for the state of one to affect the transfer of data out from the I/O pin or in from the TTL device output. For example, if the latch in the I/O port is set so that the pin is clamped low by (b), the level at 0 cannot pull P high. Conversely, if P is clamped to a low level by (c), setting the latch for a high level has no effect.

Open-Drain Configuration (Figure 5)—When the I/O port is configured as shown in figure 5, the drain connection of FET (a) is open, i.e., not connected to  $V_{DD}$  through a pull-up transistor. This option is most useful in applications where several signals (possibly several I/O port lines) are to be wire-ORed together. A common external pull-up,  $R_{L}$ , is used to establish the logic 1 levels. Another advantage of this option is that the output (point Y) can be tied through a pull-up resistor to a voltage higher than  $V_{DD}$  (clear up to  $V_{GG}$ ) for interfacing to external circuits requiring a higher logic 1 level than  $V_{DD}$  provides.

If a high level is present at point X (coming from the port latch), FET (a) will conduct and pull point Y to a low level by current flow through  $R_L$ . This low level at Y causes transistor (b) to turn on and present a low level to the input TTL circuit.

If a low level is present at X, FET (a) turns off and point Y is pulled toward  $V_{DD}$  by  $R_L$ . This causes transistor (b) to turn off and present a high level to the internal TTL circuits.

When data is input, a high level at the base of transistor (c) causes (c) to conduct and pull point Y low, with current flow through  $T_L$ . This transfers a high level to the internal I/O port logic through inverting action by the hysteresis circuit. If a

Figure 4 Standard Pull-Up Configuration

Figure 5 Open-Drain Configuration

Figure 6 Driver Pull-Up Configuration

low level is present at the base of (c), conduction stops and point Y is pulled toward  $V_{DD}$  by  $R_L$ . This is then transferred as a low level to internal I/O port logic through the hysteresis circuit.

Driver Pull-Up Configuration (Figure 6)— Figure 6 shows the I/O port driver pull-up option used to drive an LED indicator. This application is typical of a front-panel address or data display, where a row of LED indicators shows the logic state at each pin of an I/O port.

A high level at X turns FET (b) on and (a) off, providing a path for current through resistor R from the base of transistor (c). This stops (c) from conducting and the LED does not light. If a low level is present at X, (b) turns off and (a) turns

advance the shift register.

on, providing a path for current from  $V_{DD}$  through (a) to R. This current through R turns on (c), which causes the LED to conduct and be lighted.

The three options for I/O port output configurations described above are provided to aid the designer in optimizing (minimizing) the system hardware for a particular application. The choice in configuration is specified as a mask option by the designer.

During input instrucions, the trailing edge of the STROBE signal is used to indicate to the external device that the current data on the I/O port is read and new data can be changed. For example, if a shift register is connected to the I/O port, the trailing edge of the STROBE signal is used to

During output instruction, the trailing edge of this STROBE signal indicates that the new data on the I/O port latches is being changed. The output on the latches becomes true after typically 500 ns of the trailing edge of this signal.

#### Figure 7 PSU I/O Port Timing

Refer to the "Timing Characteristics" section for all signal characteristics.

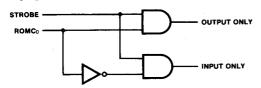

#### F3856 I/O Strobe

An additional output strobe signal is provided on the F3856 to indicate the execution of an input or output instruction for the low address I/O port on the PSU circuit. (This is port 4 of the PSU circuit with the 4-7 address.) A pulse of the duration of the WRITE clock on the STROBE pin is provided at the end of the second cycle of the I/O instruction for this port. Figure 8 shows the timing relationship of this output with respect to the execution being performed.

Although this pulse appears for both input and output instructions for this port, two different signals for input only are derived from the external gating of the STROBE and  $ROMC_0$  signals, as shown below.

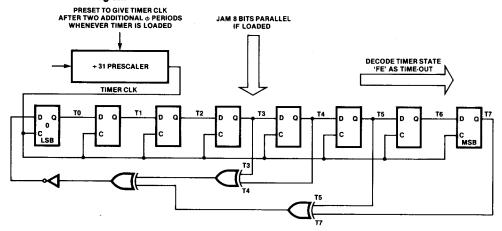

# F3851 Programmable Timer

The F3851 PSU has an 8-bit shift register, addressable as I/O port XXXXXX11, that can be used as a programmable timer (XXXXXX is the 6-bit I/O port address select, a PSU mask option). Figure 9 illustrates the shift register logic and the exclusive-OR feedback path.

Based on the logic illustrated in figure 9, binary values in the range 0 through 254, when loaded into the timer, are converted into "timer counts." As shown in table 3, "timer contents" is the actual binary value loaded into a timer, and "timer counts" is the corresponding number of time intervals the timer takes to time out. Data cannot be read out of the programmable timer I/O port.

As described in the Guide to Programming the F8 Microcomputer, an assembly-language program specifies timer counts, and the assembler converts timer counts into the binary value that must be loaded into the programmable timer. This is the value given under "Contents" in table 3. To

Figure 8 I/O Instruction Fetch and Strobe Timing

Figure 9 F3851 Timer Block Diagram

use a programmable timer, bypassing assembly-language programming, load the programmable timer with the value given under "Contents" in table 3 to time out after the number of intervals given under "Counts."

It is also possible to write small subroutines that calculate time values one count faster or slower than a given value. Such subroutines would be used if programmed delays are required.

The OUT or OUTS instruction is used to load timer counts into the programmable timer. The contents of the programmable timer cannot be read using an IN or INS instruction. The timer times out after a time interval given by the product (period of \$\phi\$ clock \timer counts) \times 31). For example, a value of 200 (11001000, or H'C8') loaded into the programmable timer becomes 215 timer counts. The timer, therefore, times out in 3.33 ms, if the period of clock signal \$\phi\$ is 500 ns.

A value of 255 (H'FF') loaded into a programmable timer stops the timer.

All timers run continuously, unless they have been stopped by loading H'FF' into the timer. Upon timing out, the timer transmits an interrupt request to the interrupt logic. If proper interrupt logic conditions exist, the timer interrupt request is passed on to the CPU through the INT REQ signal.

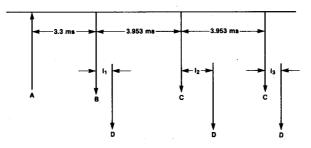

After a programmable timer has timed out, it again times out after 255 timer counts; therefore, if the programmable timer is left running, it times out every 7905 \$\phi\$ clock periods, or every 3.953 ms for a 500 ns clock.

If the timer is actually loaded with a zero value, it times out in 24 counts, whereas, once it has timed out, it next times out in 255 counts; i.e., a time-out is not the same thing as counting down to zero.

When the timer and timer interrupt are being set to time a new interval, the timer is always loaded before enabling the timer interrupt. Loading the timer clears any pending timer interrupts. When the timer interrupt is enabled, any pending

timer interrupt is acknowledged and forwarded to the CPU. Since the timer runs continuously, unless stopped under program control, enabling the timer before loading a time count can cause errors. Prior time-outs of the timer are latched in the interrupt logic of the PSU, even while timer interrupts are disabled. When the timer is enabled, an immediate interrupt acknowledge occurs if, by chance, the continuous-running timer happens to time out while timer interrupts are disabled.

If the timer is loaded just before enabling timer interrupts, loading the timer clears pending timer interrupts. Now a spurious interrupt request does not exist when the timer interrupt is enabled.

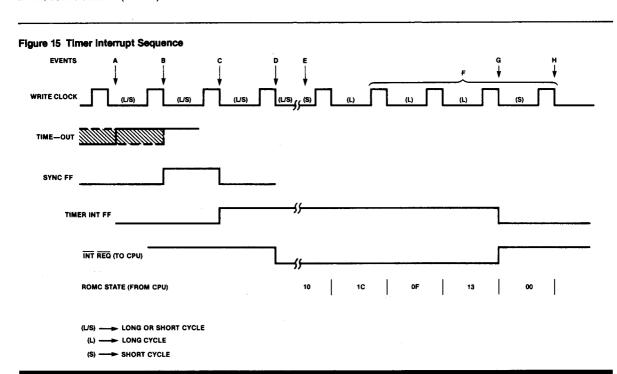

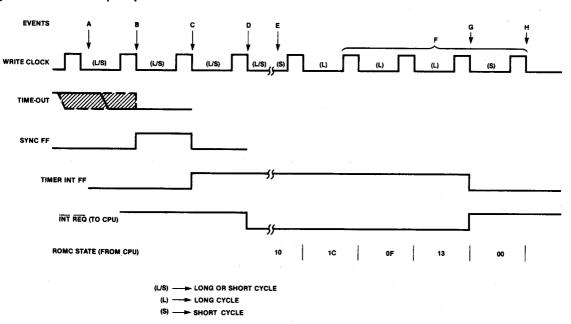

Figure 10 illustrates a possible signal sequence for a timer that is initially loaded with 200, then allowed to run continuously.

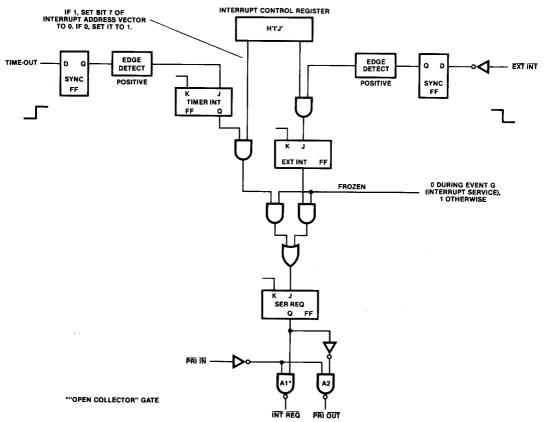

#### F3851 Interrupt Control Register

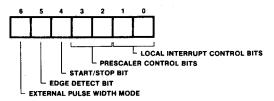

The interrupt control register (ICR) has the I/O port address XXXXXX10 (where XXXXXX is the 6-bit I/O port address select). Data is loaded into this register (I/O port) using an OUT or OUTS instruction. Data cannot be read out of this register. The contents of the ICR are interpreted as follows:

| Contents of I/O Port | Interpretation                                       |

|----------------------|------------------------------------------------------|

| B'XXXXXX00'          | Disable all interrupts                               |

| B'XXXXXX01'          | Enable external interrupt, disable timer interrupt   |

| BXXXXXX10            | Disable all interrupts                               |

| B'XXXXXX11'          | Disable external interrupt<br>enable timer interrupt |

Figure 10 Time-Out and Interrupt Request Timing

<sup>200</sup> LOADED INTO TIMER B — FIRST TIME OUT

Table 3 F3851 Timer Counts

| Counts          |                                                             |                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|-----------------|-------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| to<br>Interrupt | Contents<br>of<br>Counter                                   | Counts<br>to<br>Interrupt                                                                                                                                                                                                                                  | Contents<br>of<br>Counter                                                                                                                                                                                                                                                                                                                                                                | Counts<br>to<br>interrupt                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Contents<br>of<br>Counter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Counts<br>to<br>Interrupt                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 254             | 4D                                                          | 189                                                                                                                                                                                                                                                        | D2                                                                                                                                                                                                                                                                                                                                                                                       | 124                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 9F                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 59                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                 | 9A                                                          | 188                                                                                                                                                                                                                                                        | A5                                                                                                                                                                                                                                                                                                                                                                                       | 123                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 3D                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 58                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 252             | 34                                                          | 187                                                                                                                                                                                                                                                        | 4B                                                                                                                                                                                                                                                                                                                                                                                       | 122                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 7C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 57                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 251             | 69                                                          | 186                                                                                                                                                                                                                                                        | . 96                                                                                                                                                                                                                                                                                                                                                                                     | 121                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | F8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 56                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 250             | D3                                                          | 185                                                                                                                                                                                                                                                        | 2D                                                                                                                                                                                                                                                                                                                                                                                       | 120                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | F1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 55                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 249             | A7                                                          | 184                                                                                                                                                                                                                                                        | 5B                                                                                                                                                                                                                                                                                                                                                                                       | 119                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | E2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 54                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 248             | 4F                                                          | 183                                                                                                                                                                                                                                                        | B7                                                                                                                                                                                                                                                                                                                                                                                       | 118                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | C5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 53                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 247             | 9E                                                          | 182                                                                                                                                                                                                                                                        | 6E                                                                                                                                                                                                                                                                                                                                                                                       | 117                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 8A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 52                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 246             | 3C                                                          | - 181                                                                                                                                                                                                                                                      | DD                                                                                                                                                                                                                                                                                                                                                                                       | 116                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 51                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |